herunterladen

AN-827

APPLICATION NOTE

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

Rev. 0 | Page 1 of 8

A Resonant Approach to Interfacing Amplifiers to Switched-Capacitor ADCs

by Eric Newman and Rob Reeder

INTRODUCTION

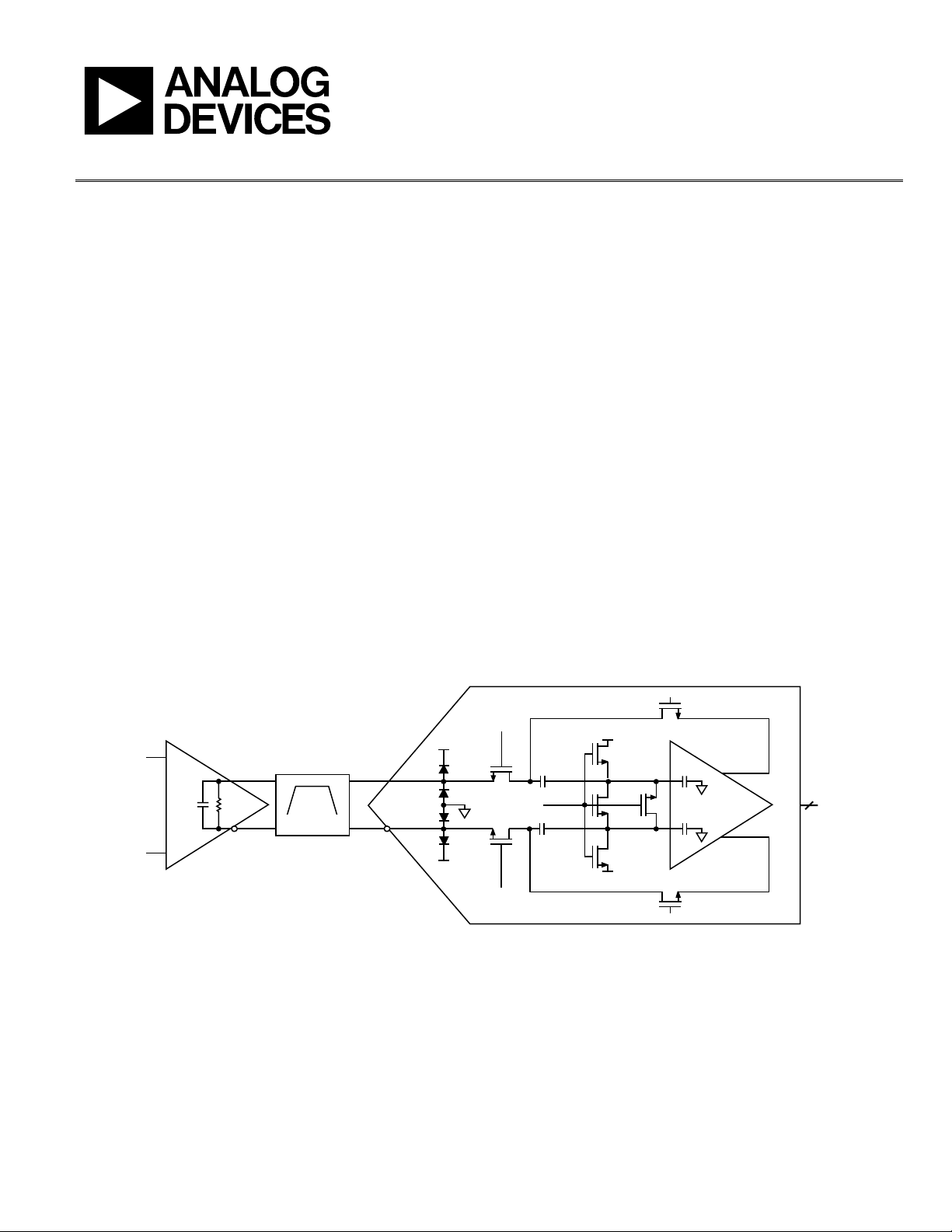

High sampling rate analog-to-digital converters (ADCs) are

commonly used to sample complex modulated signals at

intermediate frequencies in modern wireless receiver designs.

Often CMOS switched-capacitor based ADCs are selected for

such designs due to their attractive low cost and power

dissipation. These ADCs utilize an unbuffered front end

directly coupled to the sampling network, which presents time

varying input track-and-hold impedances to the amplifier

driving the ADC. To effectively drive the ADC with minimal

noise and distortion degradation of the wanted signal, it is

necessary to design a passive network interface, which helps to

reject wideband noise and transforms the track-and-hold

impedance to present a more benign load impedance to the

driving amplifier. A resonant approach for transforming the

track-and-hold impedance to a more predictable load allowing

precise design of antialiasing filters is presented at several

common IF frequencies.

SWITCHED-CAPACITOR ADCS

Switched-capacitor ADCs are different from buffered input

ADCs because the buffer is stripped out of the ADC for lower

power. The ADC sample-and-hold amplifier circuit (SHA)

comprises an input switch, an input sampling capacitor, a

sampling switch, and an amplifier. As shown in

Figure 1, the

input switch directly connects the driver to the sampling

capacitor. When the input switch is on (track mode), the driver

circuit drives the input capacitor. The input is sampled

(captured) on the input capacitor at the end of this mode. When

the input switch is off (hold mode), the driver is isolated from

the input capacitor. The track-mode period and the hold-mode

period of the ADC are approximately equal durations.

ADC

SHA

V

BIAS

V

BIAS

AV

CC

AV

CC

GND

AIN

~AIN

n

ESD

ESD

HOLD SWITCH

HOLD SWITCH

AMP

RC

INTERNAL

INPUT

CLOCK

INTERNAL

INPUT

CLOCK

INPUT

SWITCH

INPUT

SWITCH

BPF

INTERNAL

SAMPLE

CLOCK

SAMPLING

SWITCHES

SAMPLING

CAP

SAMPLING

CAP

05012-001

Figure 1. Simplified Input Model of a Switched-Capacitor ADC

Connected to Amplifier Driver