herunterladen

Keywords:

Jitter, Wander, G.703, Timing Unit, Jitter Attenuator, E1

APPLICATION NOTE 6352

DESIGN CONSIDERATIONS FOR USING THE DS26504 JITTER ATTENUATOR

Abstract: How to use DS26504 Jitter Attenuator to avoid phase slip and wander.

Overview

Building integrated timing supply (

BITS) is one type of clock used extensively in network synchronization. It is a master timing supply for all deployed equipment within a

network that requires synchronization. DS26504 is a BITS clock-recovery element that can be used in these applications. The receiver portion of this device can recover a

clock from T1, E1, 64kHz composite clock (64KCC), and 6312kHz synchronization timing interfaces.

One of the important blocks of

DS26504 is its Jitter Attenuator which operates without a dedicated crystal and uses MCLK for its operation. A crystal-less jitter attenuator with

bypass mode for T1 and E1 operation is included in DS26504.

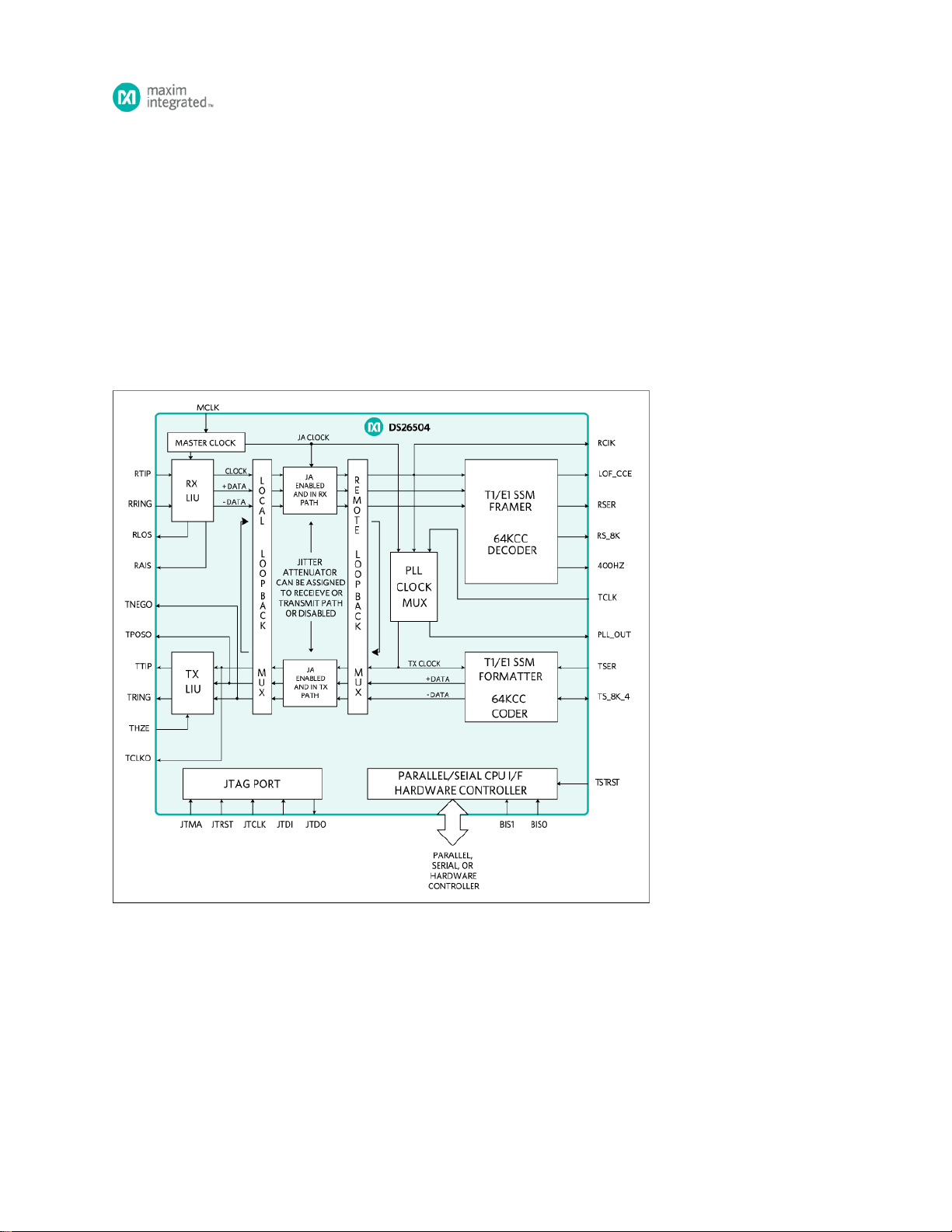

The jitter attenuator as show in

Figure 1 can be inserted either in the transmit or receive path.

Figure 1. DS26504 block diagram.

Register line interface control 1 (LIC1) (

Figure 2) allows the customer to select the position of the jitter attenuator (either in Rx or Tx path) and switch the jitter attenuator on

or off. Moreover, the jitter attenuator can be set to a depth of either 32 bits or 128 bits through the JABDS bit (LIC1.2). The 128-bit mode is used in applications where large

excursions of wander are expected. The 32-bit mode is used in delay-sensitive applications.

Page 1 of 4