herunterladen

www.latticesemi.com

1

an6059_01.1

ispPAC-POWR1208P1 Evaluation Board

PAC-POWR1208P1-EV

March 2007 Application Note AN6059

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Introduction

The Lattice Semiconductor ispPAC

®

-POWR1208P1 In-System-Programmable Analog Circuit allows designers to

implement both the analog and digital functions of a power supply monitoring and sequencing subsystem within a

single integrated circuit. By integrating analog functions such as comparators and programmable slew rate FET

drivers with the digital functionality of a Programmable Logic Device (PLD), the ispPAC-POWR1208P1 provides the

power-supply designer with a rich set of features in a single device.

ISP™ (In-System-Programmability) provides the designer with an unprecedented level of flexibility, allowing him to

configure analog parameters such as threshold voltages as well as defining state machines and combinatorial logic

functions. All configuration data is stored internally in E

2

CMOS

®

nonvolatile memory. Programming a configuration

is accomplished through an industry-standard JTAG IEEE 1149.1 interface.

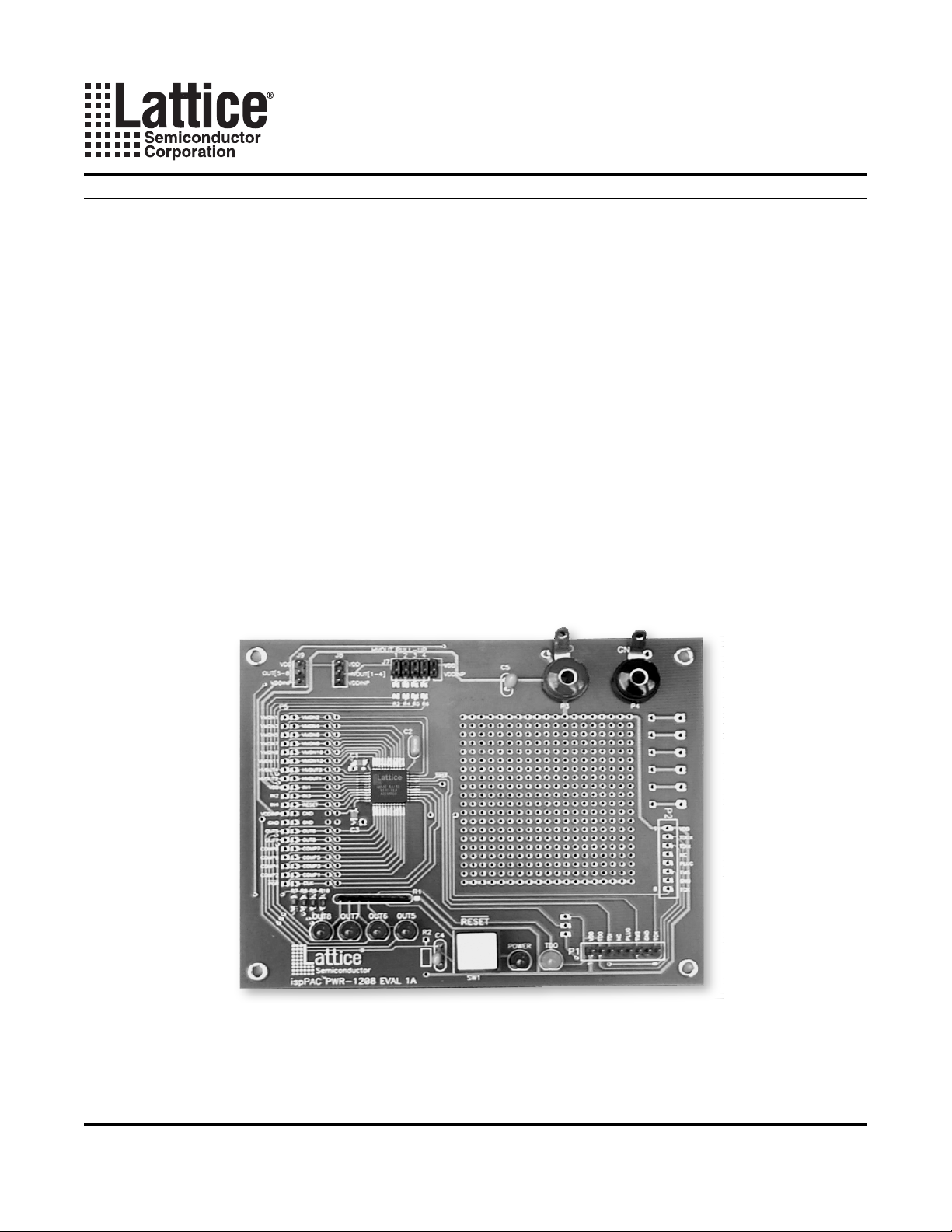

PAC-POWR1208P1-EV Evaluation Board

The PAC-POWR1208P1-EV evaluation board (Figure 1) allows the designer to quickly configure and evaluate the

ispPAC-POWR1208P1 on a fully assembled printed-circuit board. The double-sided board supports a 44-pin TQFP

package, a header for user I/O, a JTAG programming cable connector, and an uncommitted pad array for user pro-

totyping. JTAG programming signals can be generated by using an ispDOWNLOAD

®

programming cable con-

nected between the evaluation board and a PC’s parallel (printer) port. Both analog and digital features of the

ispPAC-POWR1208P1 can be easily configured using PAC-Designer

®

software.

Figure 1. PAC-POWR1208P1-EV Evaluation Board