herunterladen

© Semiconductor Components Industries, LLC, 2016

July, 2016 − Rev. 7

1 Publication Order Number:

MC100LVEL51/D

MC100LVEL51

3.3V ECL Differential Clock

D Flip‐Flop

Description

The MC100LVEL51 is a differential clock D flip-flop with reset. The

device is functionally equivalent to the EL51 device, but operates from

a 3.3 V supply. With propagation delays and output transition times

essentially equal to the EL51, the LVEL51 is ideally suited for those

applications which require the ultimate in AC performance at 3.3 V V

CC

.

The reset input is an asynchronous, level triggered signal. Data enters

the master portion of the flip-flop when the clock is LOW and is

transferred to the slave, and thus the outputs, upon a positive transition of

the clock. The differential clock inputs of the LVEL51 allow the device to

be used as a negative edge triggered flip-flop.

The differential input employs clamp circuitry to maintain stability

under open input conditions. When left open, the CLK input will be

pulled down to V

EE

and the CLK input will be biased at V

CC

/2.

Features

• 475 ps Propagation Delay

• 2.8 GHz Toggle Frequency

• ESD Protection: > 4 kV Human Body Model,

> 200 V Machine Model

• The 100 Series Contains Temperature Compensation

• PECL Mode Operating Range: V

CC

= 3.0 V to 3.8 V

with V

EE

= 0 V

• NECL Mode Operating Range: V

CC

= 0 V

with V

EE

= −3.0 V to −3.8 V

• Internal Input Pulldown Resistors

• Meets or Exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

• Moisture Sensitivity Level

♦ Level 1 for SOIC−8 NB

♦ Level 3 for TSSOP−8

♦ Level 1 for DFN−8

♦ For Additional Information, see Application Note AND8003/D

• Flammability Rating: UL 94 V−0 @ 0.125 in,

Oxygen Index: 28 to 34

• Transistor Count = 114 devices

• These Devices are Pb-Free, Halogen Free and are RoHS Compliant

*For additional marking information, refer to

Application Note AND8002/D

.

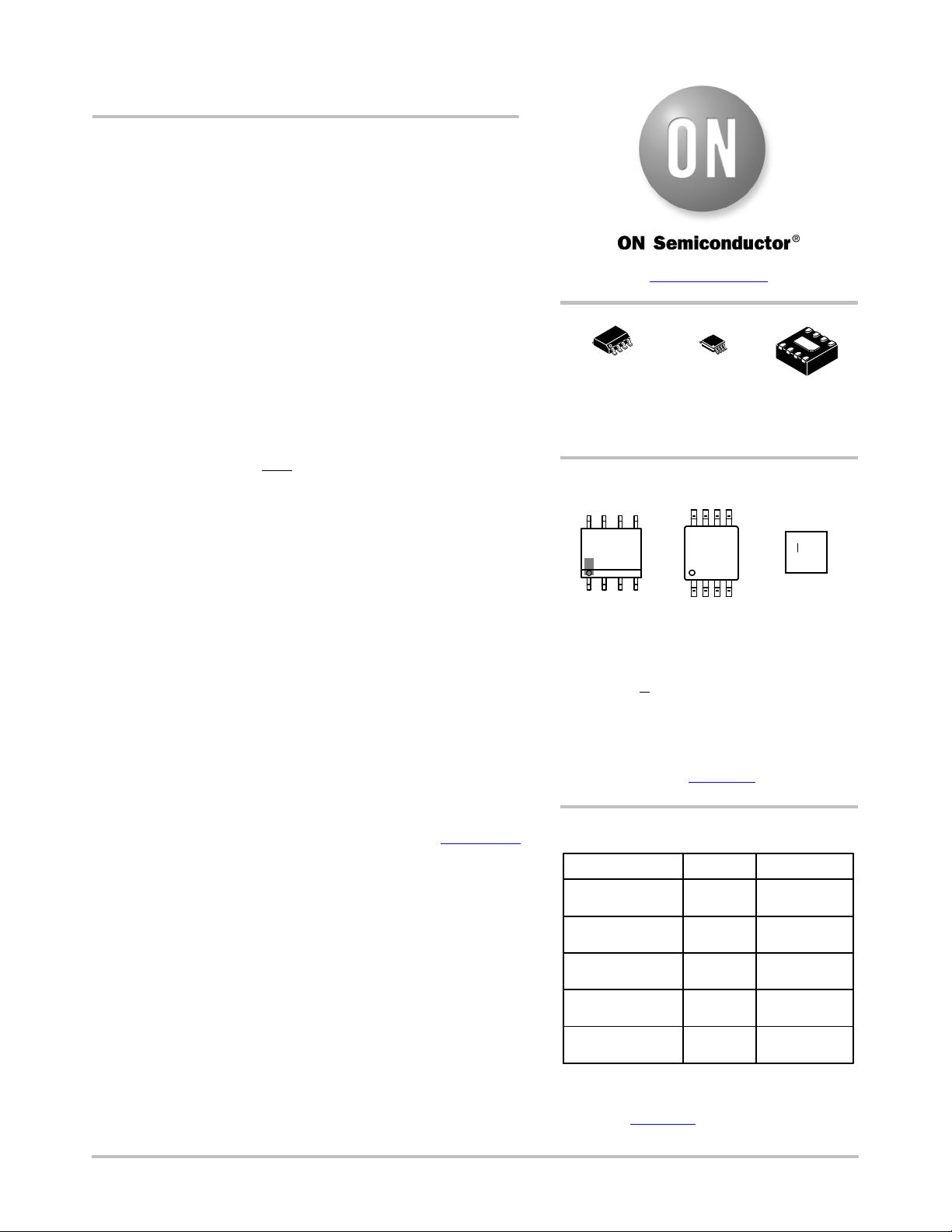

MARKING DIAGRAMS*

KV51

ALYWG

G

SOIC−8 NB

D SUFFIX

CASE 751

1

8

TSSOP−8

DT SUFFIX

CASE 948R

1

8

1

8

www.onsemi.com

KVL51

ALYW

G

1

8

DFN−8

MN SUFFIX

CASE 506AA

4G M G

G

14

(Note: Microdot may be in either location)

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

M

= Date Code

G = Pb-Free Package

SOIC−8 TSSOP−8 DFN−8

†For information on tape and reel specifications, in-

cluding part orientation and tape sizes, please refer

to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D

.

ORDERING INFORMATION

Device Package Shipping

†

MC100LVEL51DG SOIC−8 NB

(Pb-Free)

98 Units/Tube

MC100LVEL51DR2G SOIC−8 NB

(Pb-Free)

2500/Tape & Reel

TSSOP−8

(Pb-Free)

MC100LVEL51DTR2G 2500/Tape & Reel

TSSOP−8

(Pb-Free)

MC100LVEL51DTG 100 Units/Tube

DFN−8

(Pb-Free)

MC100LVEL51MNR4G 1000/Tape & Reel

Verzeichnis

- ・ Konfiguration des Pinbelegungsdiagramms on Seite 2

- ・ Abmessungen des Paketumrisses on Seite 7 Seite 8 Seite 9

- ・ Paket-Footprint-Pad-Layout on Seite 7 Seite 9

- ・ Teilenummerierungssystem on Seite 1 Seite 9

- ・ Markierungsinformationen on Seite 1 Seite 6 Seite 9

- ・ Typisches Anwendungsschaltbild on Seite 2

- ・ Technische Daten on Seite 1

- ・ Teilenummernliste on Seite 3