herunterladen

Application Note

October 2001

©2003 Silicon Storage Technology, Inc.

S72005-03-000 3/03

1

The SST logo and SuperFlash are registered trademarks of Silicon Storage Technology, Inc.

MPF is a trademark of Silicon Storage Technology, Inc.

These specifications are subject to change without notice.

INTRODUCTION

Some data storage applications require flash memory

endurance, i.e., the number of Erase and Program cycles,

to be at least 1,000,000 cycles, while still meeting the stan-

dard endurance cumulative failure rate of less than 1% (ref.

IEEE-Std-1005-1998). This would mean cycling every sec-

tor within the device about once every 5 minutes for 10

years of continuous operation. In reality, most applications

only require that some portion of the address space be

cycled 1,000,000 or more times; the rest of the address

space will be cycled far fewer times. This application note

will show how the standard SST memory, with a guaran-

teed 10,000 cycle failure rate of less than 1%, can be used

in applications where a portion of the memory requires

1,000,000 endurance cycles.

Endurance Specification

In order to guarantee endurance, the manufacturer must

specify both a number of cycles for endurance and the

associated failure rate. The lot acceptance guarantee

means that if a customer samples a shipment and the

sample fails, the entire shipment may be returned to the

manufacturer. Endurance cycling is a time consuming test;

for instance, to cycle a flash device 10,000 times takes a full

day for an SST device, while other manufacturers’ devices

will take a month or longer. Customers rarely actually per-

form incoming lot acceptance inspections for endurance.

Therefore, even if a flash memory vendor provides a lot

acceptance guarantee, the user has a difficult and time

consuming task to actually perform the sample lot accep-

tance endurance testing in a practical time frame.

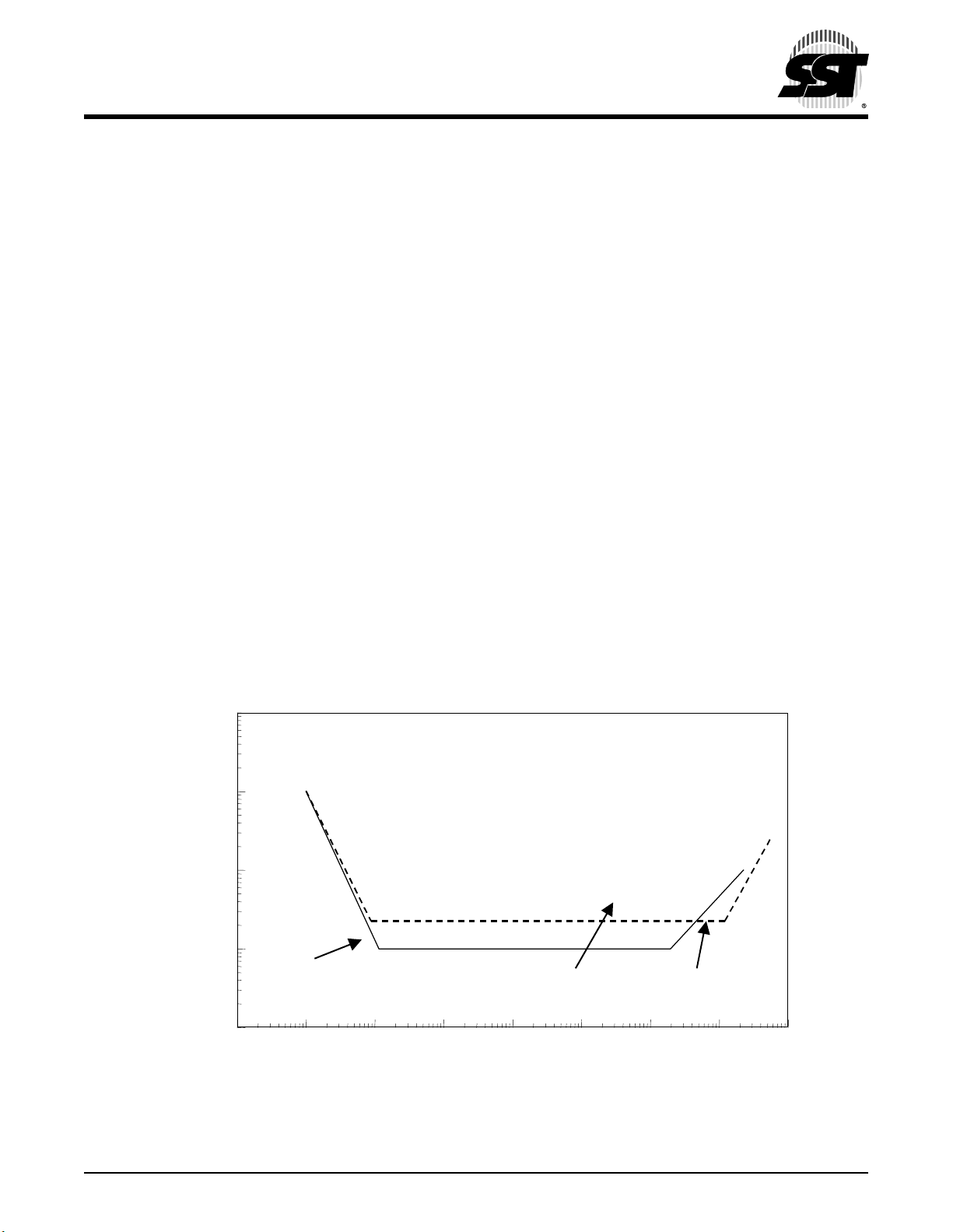

The most important value is the actual endurance failure

rate of the device in the application. This value can vary sig-

nificantly from technology to technology and per manufac-

turer for a given technology. See Figure 1 for an example of

how a “higher endurance number” does not mean a better

system failure rate. As long as the system does not actually

erase and program the device into the “wear-out” region,

the device with the lower failure rate provides better system

reliability.

SST is able to provide a true lot acceptance guarantee

(where the customer can accept/reject an entire lot based

on the results of a sample, tested under JEDEC defined

conditions) of the endurance of all SST SuperFlash mem-

ory devices. This is possible because SST’s proprietary

SuperFlash technology allows the testing of each and

every memory cell of each and every device for endurance

during the standard product testing operation.

FIGURE 1: SST’

S SPLIT-GATE AND OTHERS’ STACKED GATE CELLS USE FN TUNNELING FOR ERASE AND

CHE

FOR PROGRAM

111E-1 1E+0 1E+1 E+2 E+3 1E+4 1E+5 1E+6 1E+7

1E-4

1E-3

1E-2

1E-1

SST

Worst Stacked Gate

Cumulative Endurance Cycles

Endurance Failure Rate (%/1K cycles)

Best Stacked Gate

.......................................................

2005 F01.1

Million Cycle Endurance

Million Cycle Endurance