herunterladen

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

XRT91L31

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

JULY 2008 REV. 1.0.2

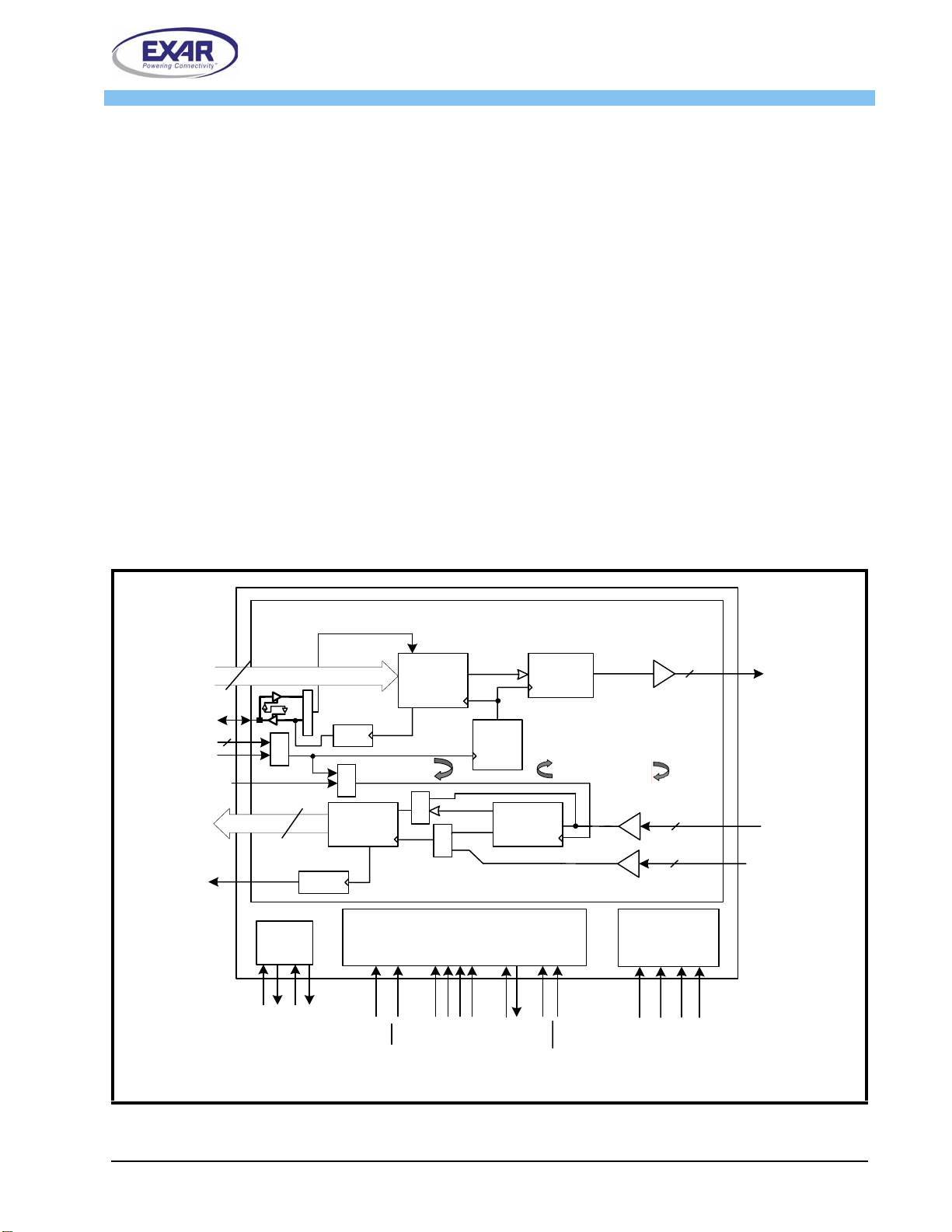

GENERAL DESCRIPTION

The XRT91L31 is a fully integrated SONET/SDH

transceiver for SONET/SDH 622.08 Mbps STS-12/

STM-4 or 155.52 Mbps STS-3/STM-1 applications.

The transceiver includes an on-chip Clock Multiplier

Unit (CMU), which uses a high frequency Phase-

Locked Loop (PLL) to generate the high-speed

transmit serial clock from a slower external clock

reference. It also provides Clock and Data Recovery

(CDR) function by synchronizing its on-chip Voltage

Controlled Oscillator (VCO) to the incoming serial

data stream. The internal CDR unit can be disabled

and bypassed in lieu of an externally recovered

received clock from the optical module. Either the

internally recovered clock or the externally recovered

clock can be used for loop timing applications. The

chip provides serial-to-parallel and parallel-to-serial

converters using an 8-bit wide LVTTL system

interface in both receive and transmit directions.

The transmit section includes an option to accept a

parallel clock signal from the framer/mapper to

synchronize the transmit section timing. The device

can internally monitor Loss of Signal (LOS) condition

and automatically mute received data upon LOS. An

on-chip SONET/SDH frame byte and boundary

detector and frame pulse generator offers the ability

recover SONET/SDH framing and to byte align the

receive serial data stream into the 8-bit parallel bus.

APPLICATIONS

• SONET/SDH-based Transmission Systems

• Add/Drop Multiplexers

• Cross Connect Equipment

• ATM and Multi-Service Switches, Routers and

Switch/Routers

• DSLAMS

• SONET/SDH Test Equipment

• DWDM Termination Equipment

FIGURE 1. BLOCK DIAGRAM OF XRT91L31

Reset

DLOOP

RLOOPS

LOOPTIME

LOSEXT

STS-12/STS-3

ALOOP

DLOSDIS

FRAMEPULSE

OOF

Clock Control

Control Block

CDRDIS

CDRREFSEL

CMUFREQSEL

STS-12/STM-4 or STS-3/STM-1

TRANSCEIVER

Loop Filters

CAP1P

CAP2P

CAP1N

CAP2N

RXDO[7:0]

RXPCLKO

CDR

RXIP/N

8

Div by 8

XRXCLKIP/N

SIPO

(Serial Input

Parallel Output)

MUX

PISO

(Parallel Input

Serial Output)

DLOOP

ALOOP

RLOOPS

Re-Timer

CMU

TXOP/N

MUX

XOR

TTLREFCLK

REFCLKP/N

CDRAUXREFCLK

MUX

TXPCLK_IO

PIO_CTRL

Div by

8

ENB

ENB

TXDI[7:0]

8

MUX

Verzeichnis

- ・ Konfiguration des Pinbelegungsdiagramms on Seite 6 Seite 7 Seite 8 Seite 9 Seite 10

- ・ Abmessungen des Paketumrisses on Seite 40

- ・ Teilenummerierungssystem on Seite 3 Seite 40

- ・ Blockdiagramm on Seite 1 Seite 20 Seite 27

- ・ Beschreibung der Funktionen on Seite 1 Seite 14

- ・ Technische Daten on Seite 23

- ・ Anwendungsbereich on Seite 1 Seite 2 Seite 15

- ・ Elektrische Spezifikation on Seite 38 Seite 39