herunterladen

1

®

AN1250.0

ISL59448EVAL1Z Evaluation Board User’s Guide

Introduction

The ISL59448EVAL1Z is a RoHS compliant evaluation board

that contains all the circuitry needed to characterize critical

performance parameters of the ISL59448 triple 2:1 MUX-

amplifier, over a variety of applications.

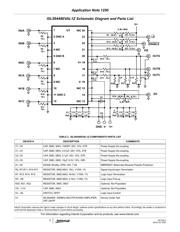

The ISL59448 contains 3 separate 2 input multiplexers, each

followed by a gain of 2 buffer controlled by common set of

logic inputs (Figure 1, Table 1). Control features include a

high speed (20ns) HIZ output control for individual selection

of MUX amps that share a common video output line. A

control logic latch (LE

) enables multiple devices to share a

common input control logic bus. The ENABLE

control can be

used to save power by powering the device down.

The evaluation board circuit and layout is optimized for

either 50Ω or 75Ω terminations, and implements a basic R-

G-B video 2 input MUX-amp. The board is supplied with 75Ω

input signal terminations and a 75Ω back-termination

resistor on each of the 3 outputs, making it suitable for

driving video cable with a throughput gain of 0dB. The user

has the option of replacing the 75Ω resistors with 50Ω

resistors for other applications. SPDT switches are included

to manually control each logic input as well as selecting on-

board logic signal termination resistors of 50Ω or 5kΩ.

The layout contains component options that include an

output capacitor to ground, a series resistor (R

S

) followed by

a parallel resistor (R

L

) capacitor (C

L

) network to ground.

This option allows the user to select several different output

configurations and to examine frequency domain and time

domain response under a variety of different layout parasitic

conditions. Examples are shown in Figures 2A, 2B, and 2C.

The evaluation board is supplied with the 75Ω back

termination resistors for video cable driving as shown in

Figure 2C.

Amplifier Performance and Output Configurations

The ISL59448 output amplifiers are designed for high

impedance inter-stage use as well as lower impedance

video cable driver applications. For example, in an inter-

stage application (Figure 2A) where the ISL59448 is driving

a high impedance amplifier or buffer, the output amplifiers

can be load over a resistance range of 150Ω to 1kΩ or

higher. They achieve their best performance with a 500Ω

load and an output capacitance to ground of 1.1pF or less.

For video cable driving applications, the optimum

performance is achieved using the 75Ω back terminated

output configuration shown in Figure 2C. Consult the device

data sheet for the performance parameters in the

application.

High Frequency Layout Considerations

At frequencies of 500MHz and higher, circuit board layout

may limit performance. The following layout guidelines are

implemented on the evaluation board;

• Signal I/O lines are the same lengths and widths to match

propagation delay and trace parasitics,

• No series connected vias are used in signal I/O lines, as

they can add unwanted inductance,

• Input and output traces use 50Ω controlled impedance,

and their lengths are minimized to reduce transmission

line effects.

• High frequency decoupling caps are places as close to the

device power supply pin as possible - without series vias

between the capacitor and the device pin.

These layout methods are difficult to achieve in practice. The

evaluation board contains additional unpopulated resistor

and capacitor pads for use as a breadboarding tool to

examine the effects of PCB layout parasitics on amplifier

performance.

Power Sequencing

Proper power supply sequencing is -V first, then +V. In

addition, the +V and -V supply pin voltage rate-of-rise must

be limited to ±1V/µs or less. The evaluation board contains

parallel-connected low Von Shottky diodes on each supply

terminal to minimize the risk of latch up due to incorrect

sequencing. In addition, extra 10µF decoupling capacitors

are added to each supply to aid in reducing the applied

voltage rate-of-rise.

Reference Documents

1. ISL59448 Data Sheet, FN6160

OUT

DECODE

IN0(A,B,C)

IN1(A,B,C)

C

LE

S0

ENABLE

D

L

Q

EN0

EN1

HIZ

A logic high on LE

will latch the last S0 state.

This logic state is preserved when cycling HIZ

or ENABLE

functions.

AMPLIFIER BIAS

C

D

L

Q

+

-

FIGURE 1. ISL59448 FUNCTIONAL BLOCK DIAGRAM

(1 OF 3 CHANNELS)

Application Note March 29, 2006

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2006. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.