herunterladen

GND

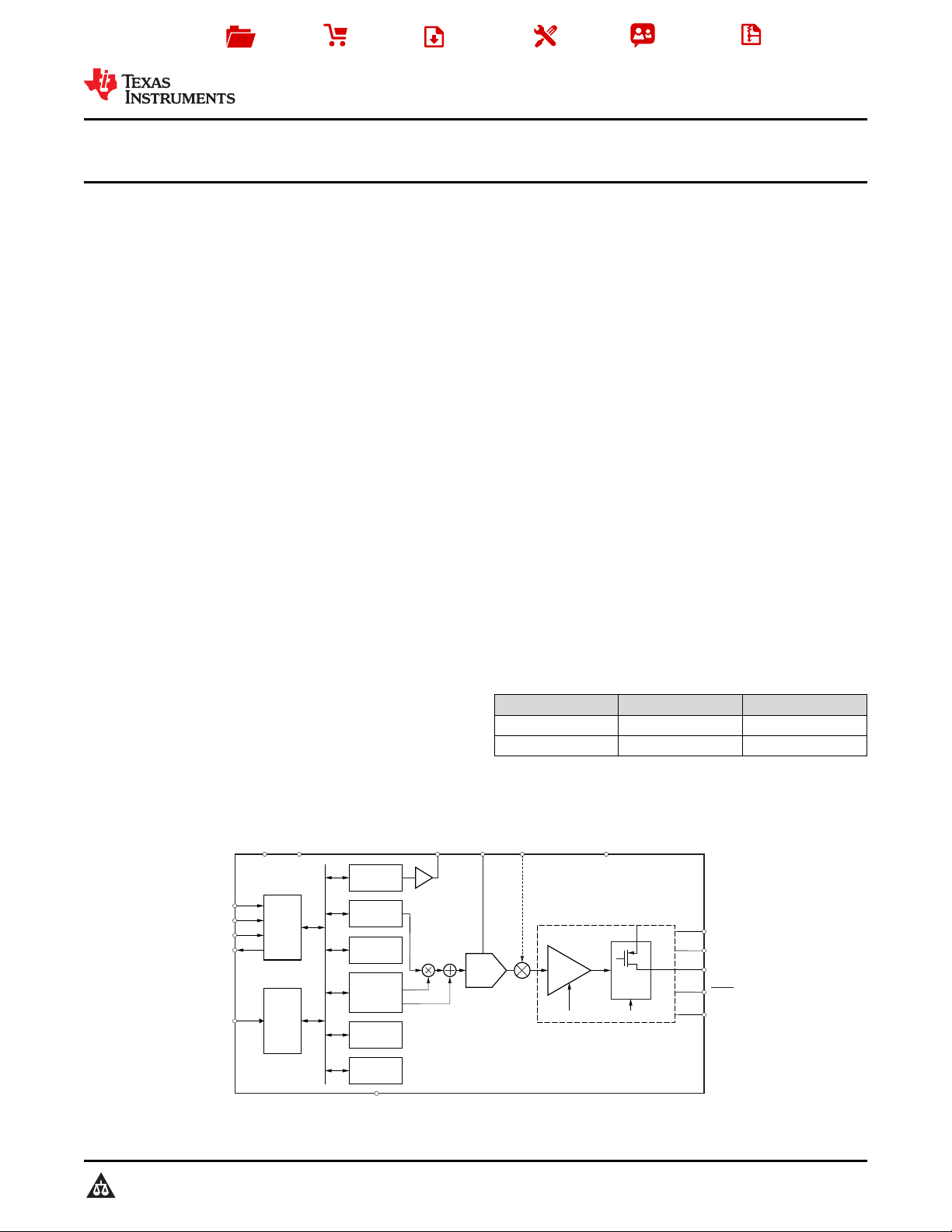

DACx750

AVDDDVDD-ENDVDD

Watchdog

Timer

Slew Rate

Control

User Calibration

Gain/Offset

Register

DAC Input

Register

Thermal

Alarm

Internal

Reference

SPI Shift Register

Input Control Logic

Control Logic

REFOUT

REFIN HART-IN

LATCH

SCLK

DIN

SDO

CLR

DAC

Pre-

Conditioning

Current

Source

I

ENABLE

ISET-R

I

GAIN

Current Output Stage

IOUT

ALARM

BOOST

R3-SENSE

Copyright © 2016, Texas Instruments Incorporated

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

Reference

Design

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

DAC7750

,

DAC8750

SBAS538B –DECEMBER 2013–REVISED JUNE 2016

DACx750 Single-Channel, 12- and 16-Bit Programmable Current Output

Digital-to-Analog Converters for 4-mA to 20-mA Current Loop Applications

1

1 Features

1

• Current Output Options:

– 0 mA to 24 mA

– 4 mA to 20 mA

– 0 mA to 20 mA

• ±0.1% FSR Typical Total Unadjusted Error (TUE)

• DNL: ±1 LSB Maximum

• Max Loop Compliance Voltage: AVDD – 2 V

• Internal 5-V Reference: 10 ppm/°C (Maximum)

• Internal 4.6-V Power-Supply Output

• CRC Frame Error Check

• Watchdog Timer

• Thermal Alarm

• Open Circuit Alarm

• Terminals to Monitor Output Current

• On-Chip Fault Alarm

• User-Calibration for Offset and Gain

• Wide Temperature Range: –40°C to 125°C

• 6-mm × 6-mm 40-Pin VQFN and 24-Pin HTSSOP

Packages

2 Applications

• 4-mA to 20-mA Current Loops

• Analog Output Modules

• Building Automation

• Environment Monitoring

• Programmable Logic Controllers (PLCs)

• Field Sensors and Process Transmitters

3 Description

The DAC7750 and DAC8750 are low-cost, precision,

fully-integrated 12-bit and 16-bit digital-to-analog

converters (DACs) designed to meet the

requirements of industrial process-control

applications. These devices can be programmed as a

current output with a range of 4 mA to 20 mA, 0 mA

to 20 mA, or 0 mA to 24 mA. The DAC7750 and

DAC8750 include reliability features such as CRC

error checking on the serial peripheral interface

(SPI™) frame, a watchdog timer, an open circuit,

compliance voltage, and thermal alarm. In addition,

the output current can be monitored by accessing an

internal precision resistor.

These devices include a power-on-reset function to

ensure that the device powers up in a known state

(IOUT is disabled and in a Hi-Z state). The CLR

terminal sets the current output to the low end of the

range if the output is enabled. Program the zero and

gain registers to digitally calibrate the device in the

end system. The output slew rate is also

programmable by register. These devices can

superimpose an external HART

®

signal on the current

output, and can operate with a 10-V to 36-V supply.

All versions are available in both 40-pin VQFN and

24-pin TSSOP packages.

Device Information(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

DACx750 HTSSOP (24) 7.80 mm × 4.40 mm

DACx750 VQFN (40) 6.00 mm × 6.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Block Diagram

Verzeichnis

- ・ Konfiguration des Pinbelegungsdiagramms on Seite 3 Seite 4

- ・ Abmessungen des Paketumrisses on Seite 43 Seite 45 Seite 46

- ・ Markierungsinformationen on Seite 43 Seite 44

- ・ Blockdiagramm on Seite 1 Seite 20

- ・ Typisches Anwendungsschaltbild on Seite 36 Seite 37 Seite 38

- ・ Technische Daten on Seite 5

- ・ Anwendungsbereich on Seite 1 Seite 53

- ・ Elektrische Spezifikation on Seite 6 Seite 7 Seite 8 Seite 9 Seite 22