herunterladen

®

Altera Corporation 1

Mercury

Programmable Logic

Device Family

January 2003, ver. 2.2 Data Sheet

DS-MERCURY-2.2

Development

13

Tools

Features…

■ High-performance programmable logic device (PLD) family (see

Table 1)

– Integrated high-speed transceivers with support for clock data

recovery (CDR) at up to 1.25 gigabits per second (Gbps)

– Look-up table (LUT)-based architecture optimized for high

speed

– Advanced interconnect structure for fast routing of critical paths

– Enhanced I/O structure for versatile standards and interface

support

– Up to 14,400 logic elements (LEs)

■ System-level features

– Up to four general-purpose phase-locked loops (PLLs) with

programmable multiplication and delay shifting

– Up to 12 PLL output ports

– Dedicated multiplier circuitry for high-speed implementation of

signed or unsigned multiplication up to 16 × 16

– Embedded system blocks (ESBs) used to implement memory

functions including quad-port RAM, true dual-port RAM, first-

in first-out (FIFO) buffers, and content-addressable memory

(CAM)

– Each ESB contains 4,096 bits and can be split and used as two

2,048-bit unidirectional dual-port RAM blocks

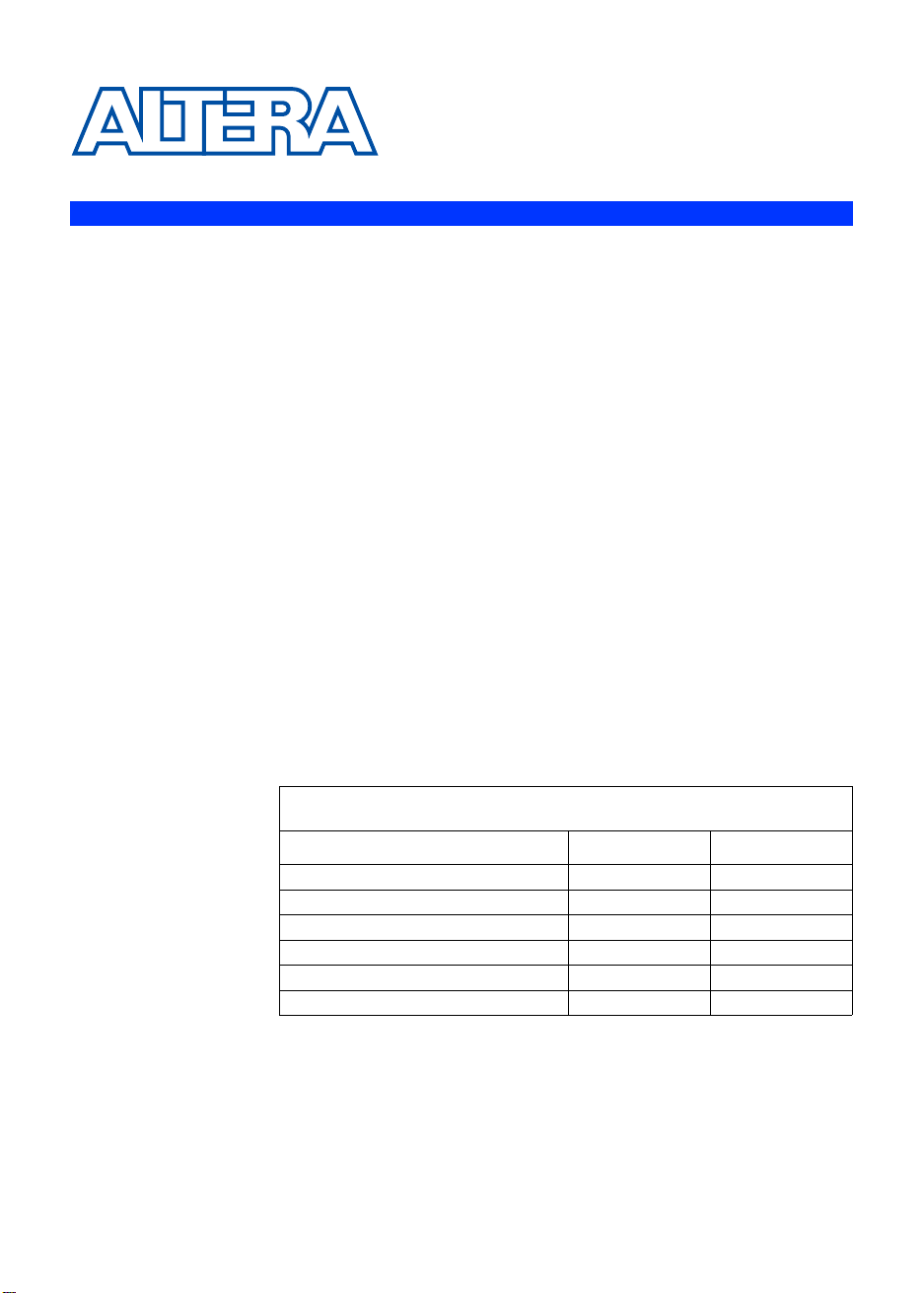

Note to Table 1:

(1) Each ESB can be used for two dual- or single-port RAM blocks.

Table 1. Mercury Device Features

Feature EP1M120 EP1M350

Typical gates 120,000 350,000

HSDI channels 8 18

LEs 4,800 14,400

ESBs (1) 12 28

Maximum RAM bits 49,152 114,688

Maximum user I/O pins 303 486

Verzeichnis