herunterladen

10kW

ADC

GŸ =Ÿ 1

R

F

R

I

Output

Stage

SPI

Interface

SCLK

DIO

CS

7

V

OUT

5

DV

DD

10

AV

DD

1

GND

6

V

REF

4

3

8

9

MSP430

Microcontroller

+3V

+5V

V

REF

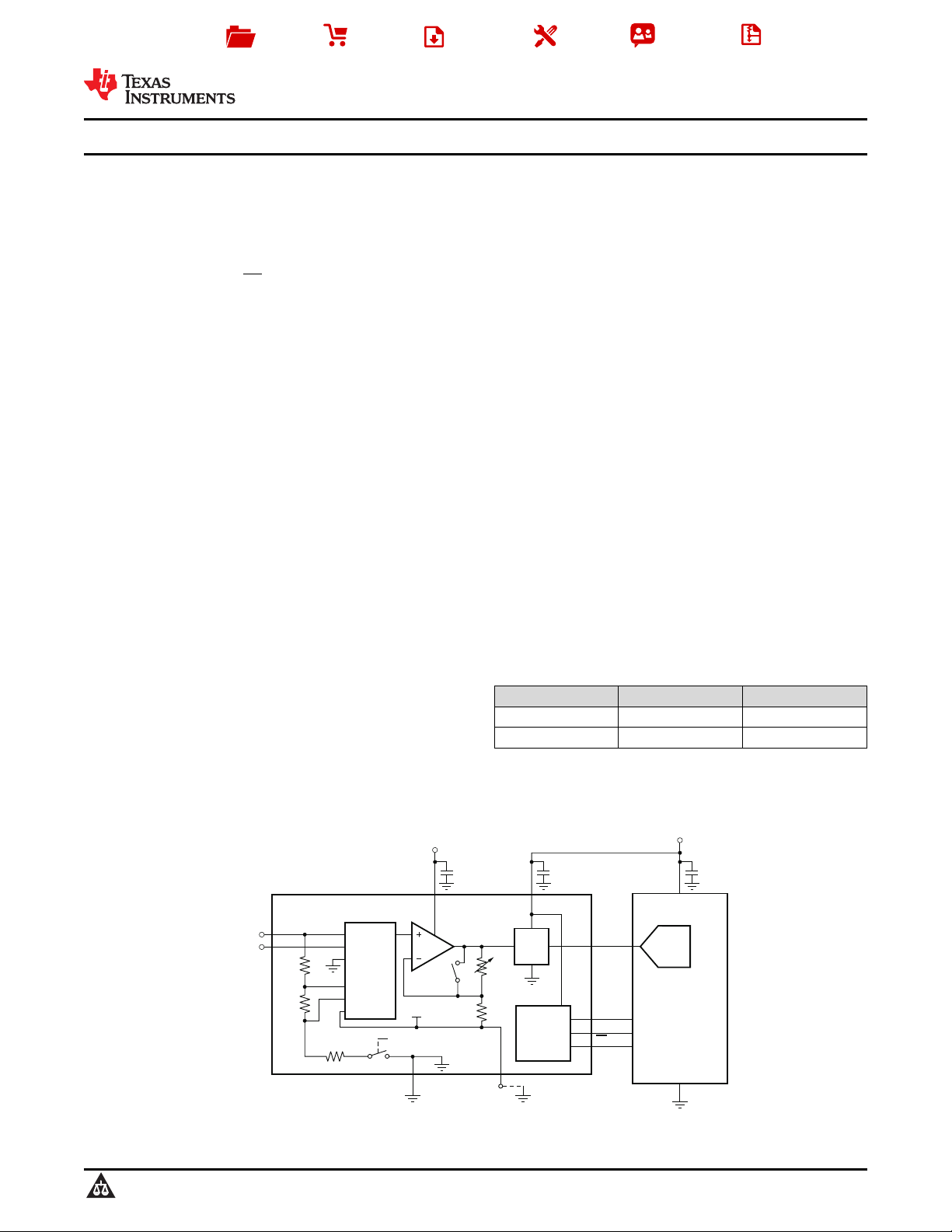

PGA112

PGA113

V /CH0

CAL

2

CH1

CAL3

CAL4

CAL1

CAL2

0.1V

CAL

0.9V

CAL

10kW

80kW

MUX

CAL2/3

C

0.1 F

BYPASS

m

C

0.1 F

BYPASS

m

C

0.1 F

BYPASS

m

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

Reference

Design

PGA112

,

PGA113

,

PGA116

,

PGA117

SBOS424C ãMARCH 2008ãREVISED NOVEMBER 2015

PGA11x Zerû¡-Drift Programmable Gain Amplifier With Mux

1 Features 2 Applications

1

ã Rail-to-Rail Input and Output

ã Remote e-Meter Reading

ã Offset: 25 ö¥V (Typical), 100 ö¥V (Maximum) ã Automatic Gain Control

ã Zerû¡ Drift: 0.35 ö¥V/ô¯C (Typical), 1.2 ö¥V/ô¯C ã Portable Data Acquisition

(Maximum)

ã PC-Based Signal Acquisition Systems

ã Low Noise: 12 nV/ãHz

ã Test and Measurement

ã Input Offset Current: ôÝ5 nA Maximum (25ô¯C)

ã Programmable Logic Controllers

ã Gain Error: 0.1% Maximum (G ãÊ 32),

ã Battery-Powered Instruments

0.3% Maximum (G > 32)

ã Handheld Test Equipment

ã Binary Gains: 1, 2, 4, 8, 16, 32, 64, 128 (PGA112,

PGA116)

3 Description

ã Scope Gains: 1, 2, 5, 10, 20, 50, 100, 200

The PGA112 and PGA113 devices (binary and scope

(PGA113, PGA117)

gains) offer two analog inputs, a three-pin SPI

interface, and software shutdown in a 10-pin, VSSOP

ã Gain Switching Time: 200 ns

package. The PGA116 and PGA117 (binary and

ã 2 Channel MUX: PGA112, PGA113

scope gains) offer 10 analog inputs, a SPI interface

10 Channel MUX: PGA116, PGA117

with daisy-chain capability, and hardware and

ã Four Internal Calibration Channels

software shutdown in a 20-pin TSSOP package.

ã Amplifier Optimized for Driving CDAC ADCs

All versions provide internal calibration channels for

ã Output Swing: 50 mV to Supply Rails system-level calibration. The channels are tied to

GND, 0.9 V

CAL

, 0.1 V

CAL

, and V

REF

, respectively.

ã AV

DD

and DV

DD

for Mixed Voltage Systems

V

CAL

, an external voltage connected to Channel 0, is

ã I

Q

= 1.1 mA (Typical)

used as the system calibration reference. Binary

ã Software and Hardware Shutdown: I

Q

ãÊ 4 ö¥A

gains are: 1, 2, 4, 8, 16, 32, 64, and 128; scope gains

(Typical)

are: 1, 2, 5, 10, 20, 50, 100, and 200.

ã Temperature Range: ã40ô¯C to 125ô¯C

Device Information

(1)

ã SPIã Interface (10 MHz) With Daisy-Chain

PART NUMBER PACKAGE BODY SIZE (NOM)

Capability

PGA112, PGA113 VSSOP (10) 3.00 mm û 3.00 mm

PGA116, PGA117 TSSOP (20) 6.50 mm û 4.40 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Simplified Schematic

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Verzeichnis

- У Konfiguration des Pinbelegungsdiagramms on Seite 3 Seite 4

- У Abmessungen des Paketumrisses on Seite 50 Seite 52 Seite 53

- У Markierungsinformationen on Seite 50 Seite 51

- У Blockdiagramm on Seite 1 Seite 20 Seite 42

- У Typisches Anwendungsschaltbild on Seite 42 Seite 43 Seite 46

- У Technische Daten on Seite 5

- У Anwendungsbereich on Seite 1 Seite 31 Seite 43

- У Elektrische Spezifikation on Seite 6 Seite 7 Seite 8 Seite 31 Seite 41