herunterladen

CY22180

Very Low Jitter Field and Factory Programmable

Clock Generator

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 001-15577 Rev. *A Revised January 13, 2009

Features

■ Low period and cycle-to-cycle jitter

❐ Typical pk-pk period jitter: 60 ps

■ Wide output frequency range

❐ Commercial temperature: 20–200 MHz

❐ Industrial temperature: 20–166 MHz

■ Input frequency range

❐ External crystal: 10–30 MHz fundamental crystal

❐ External reference: 10–133 MHz clock

■ Integrated phase-locked loop (PLL)

■ Field programmable and factory programmed options

■ Programmable crystal load capacitor tuning array

■ 3.3V operation

■ Commercial and industrial temperature ranges

■ Power down or output enable function

Benefits

■ Internal PLL generates up to 200 MHz output. Can generate

custom frequencies from an external crystal or a driven source.

■ In-house programming of samples and prototype quantities

can be done using the CY3672-USB programmer and CY3619

socket adapter. Production quantities are available through

Cypress’s value added distribution partners or by using third

party programmers from BP Microsystems, HiLo Systems, and

others.

■ Eliminates the need for expensive and difficult to use

higher-order crystals.

■ Enables fine-tuning of output clock frequency by adjusting

C

Load

of the crystal. Eliminates the need for external C

Load

capacitors.

■ Application compatibility in standard and low-power systems

■ Enables low-power state or output clocks to High-Z state

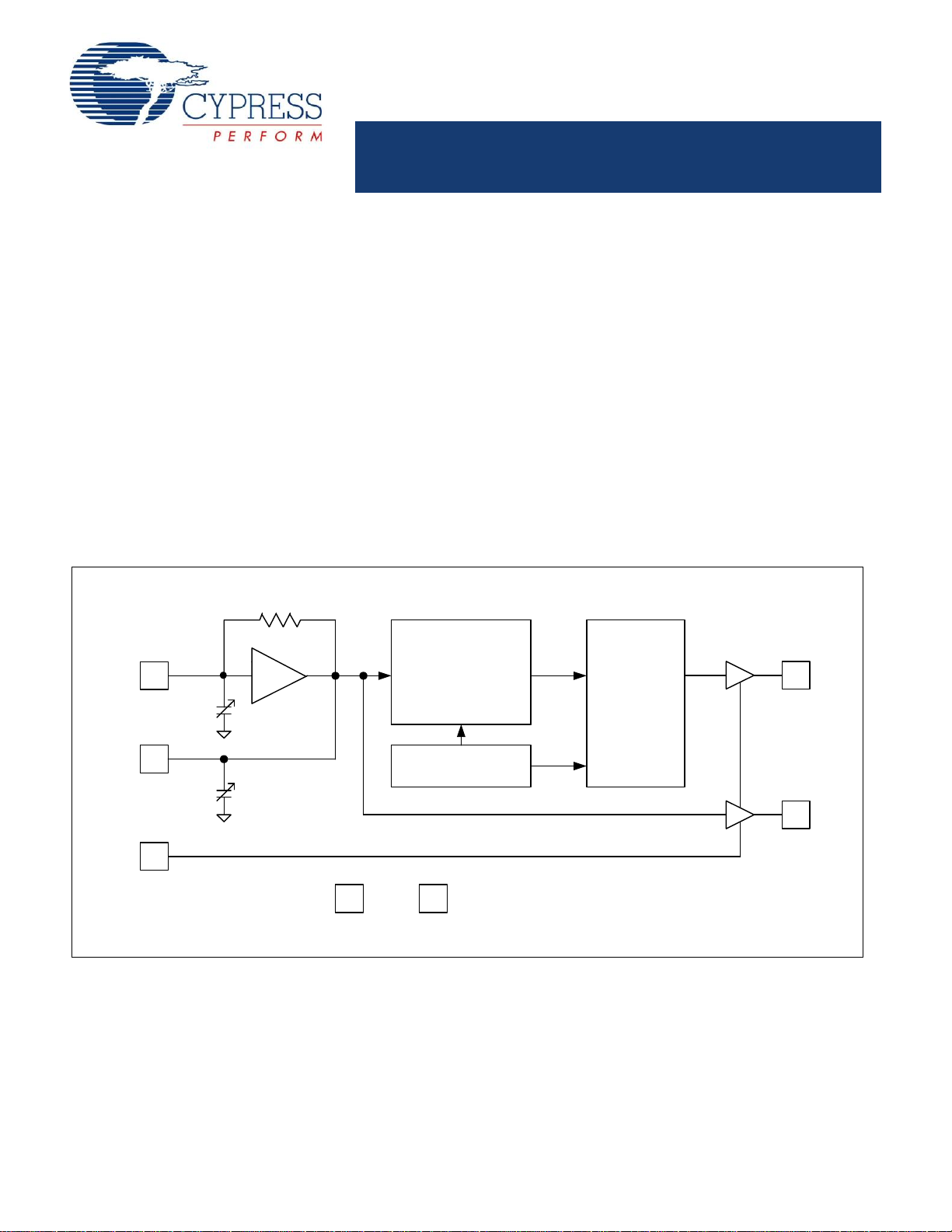

PLL

PROGRAMMABLE

CONFIGURATION

OUTPUT

DIVIDER

1

8

3

2 4

5

6

VDD VSS

CLKOUT

REFOUT

XOUT

XIN/CLKIN

PD# or OE

C

XOUT

CXIN

Logic Block Diagram

[+] Feedback

Verzeichnis