herunterladen

CY2544/CY2548, CY2546

Quad PLL Programmable Clock Generator

with Spread Spectrum

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 001-12563 Rev. *G Revised December 21, 2010

Quad PLL Prog rammable Clock G enerator

Features

■ Four fully integrated phase locked loops (PLLs)

■ Input frequency range

❐ External crystal: 8 to 48 MHz for CY2544 and CY2546

❐ External reference: 8 to 166 MHz clock

■ Reference clock input voltage range

❐ 2.5V, 3.0V, and 3.3V for CY2548

❐ 1.8V for CY2544 and CY2546

■ Wide operating output frequency range

❐ 3 to 166 MHz

■ Programmable spread spectrum with center and down

spread option and Lexmark and Linear modulation profiles

■ VDD supply voltage options:

❐ 2.5V, 3.0V, and 3.3V for CY2544 and CY2548

❐ 1.8V for CY2546

■ Selectable output clock voltages:

❐ 2.5V, 3.0V, and 3.3V for CY2544 and CY2548

❐ 1.8V for CY2546

■ Frequency select feature with option to select eight different

frequencies over nine clock outputs

■ Power down, output enable, and SS ON/OFF controls

■ Low jitter, high accuracy outputs

■ Ability to synthesize nonstandard frequencies with

Fractional-N capability

■ Up to nine clock outputs with programmable drive strength

■ Glitch free outputs while frequency switching

■ 24-pin QFN package

■ Commercial and Industrial temperature ranges

Benefits

■ Multiple high performance PLLs allow synthesis of unrelated

frequencies

■ Nonvolatile programming for personalization of PLL

frequencies, spread spectrum characteristics, drive strength,

crystal load capacitance, and output frequencies

■ Application specific programmable EMI reduction using

spread spectrum for clocks

■ Programmable PLLs for system frequency margin tests

■ Meets critical timing requirements in complex system

designs

■ Suitability for PC, consumer, portable, and networking

applications

■ Capable of Zero PPM frequency synthesis error

■ Uninterrupted system operation during clock frequency

switch

■ Application compatibility in standard and low power systems

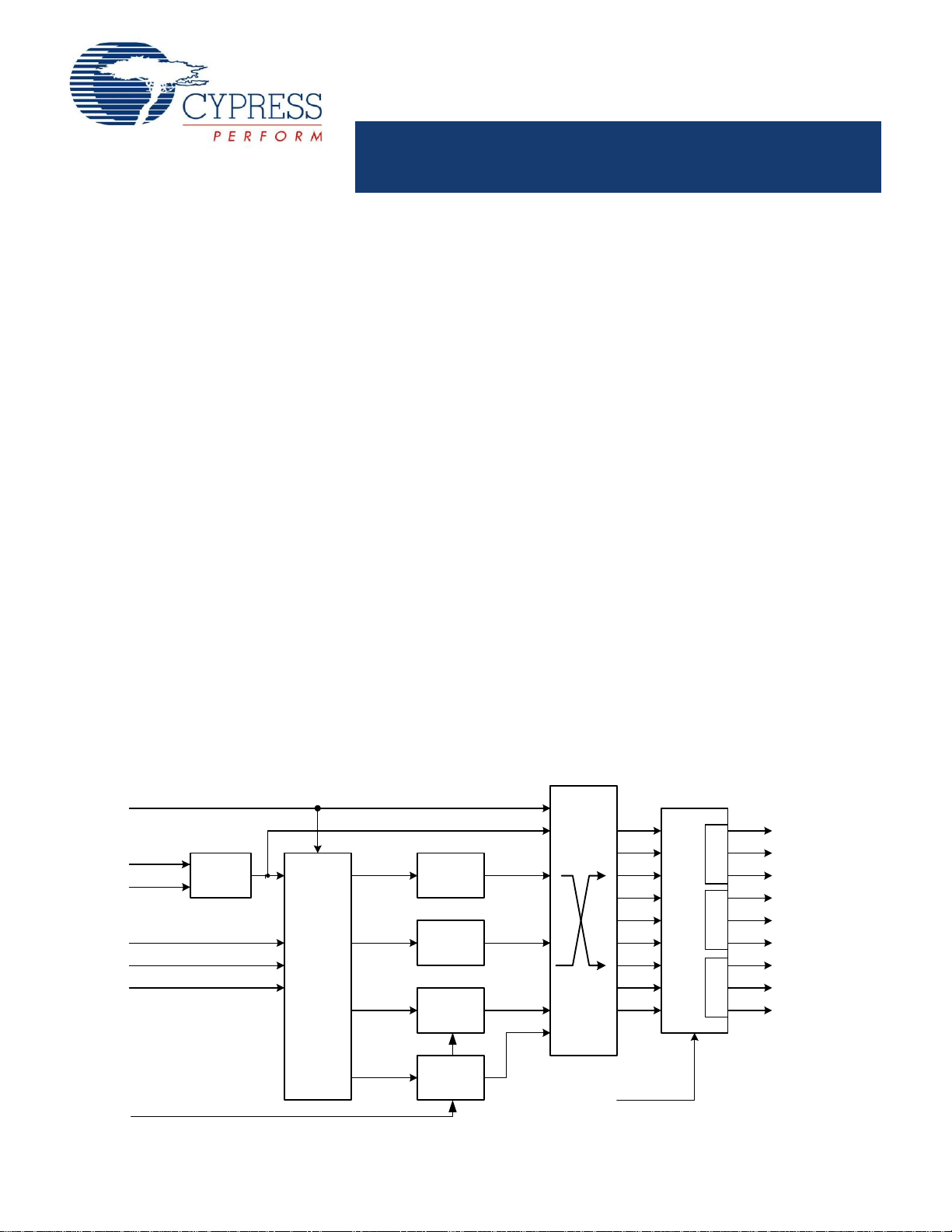

OSC

PLL1

PLL2

PLL3

(SS)

PLL4

(SS)

Output

Dividers

and

Drive

Strength

Control

CLK1

CLK9

CLK8

CLK7

CLK6

CLK5

CLK4

CLK3

CLK2

CLKIN

FS 2

FS 1

FS 0

SSON

XOUT

XIN/

EXCLKIN

PD#/OE

Bank

1

Bank

3

Bank

2

MUX

and

Control

Logic

Crossbar

Switch

Logic Block Diagram

[+] Feedback