herunterladen

®

Altera Corporation 1

ACEX 1K

Programmable Logic Device Family

May 2003, ver. 3.4 Data Sheet

DS-ACEX-3.4

Development

13

Tools

Features...

■ Programmable logic devices (PLDs), providing low cost

system-on-a-programmable-chip (SOPC) integration in a single

device

– Enhanced embedded array for implementing megafunctions

such as efficient memory and specialized logic functions

– Dual-port capability with up to 16-bit width per embedded array

block (EAB)

– Logic array for general logic functions

■ High density

– 10,000 to 100,000 typical gates (see Table 1)

– Up to 49,152 RAM bits (4,096 bits per EAB, all of which can be

used without reducing logic capacity)

■ Cost-efficient programmable architecture for high-volume

applications

– Cost-optimized process

– Low cost solution for high-performance communications

applications

■ System-level features

– MultiVolt

TM

I/O pins can drive or be driven by 2.5-V, 3.3-V, or

5.0-V devices

– Low power consumption

– Bidirectional I/O performance (setup time [t

SU

] and clock-to-

output delay [t

CO

]) up to 250 MHz

– Fully compliant with the peripheral component interconnect

Special Interest Group (PCI SIG) PCI Local Bus Specification,

Revision 2.2 for 3.3-V operation at 33 MHz or 66 MHz

■ Extended temperature range

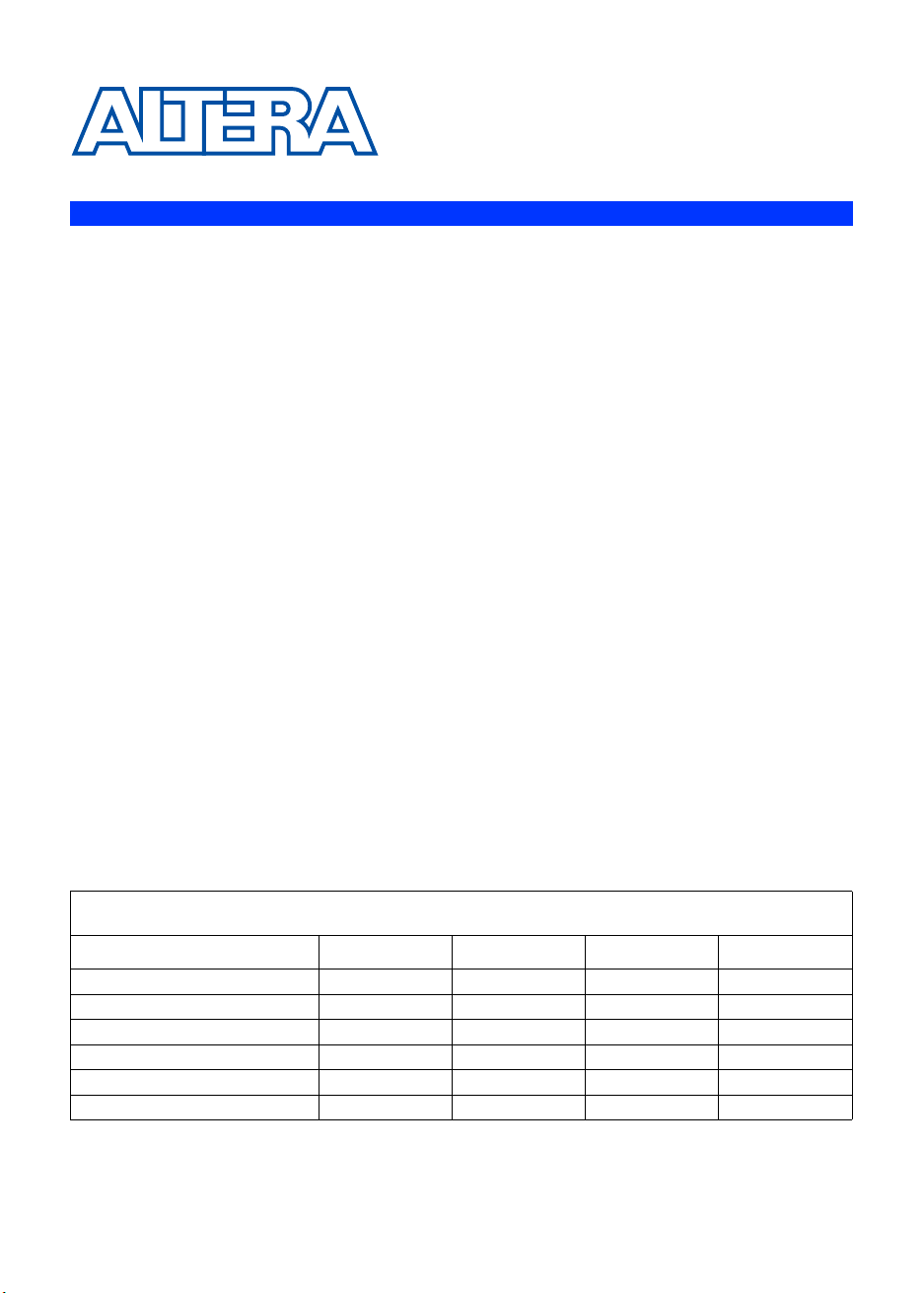

Table 1. ACEX

TM

1K Device Features

Feature EP1K10 EP1K30 EP1K50 EP1K100

Typical gates 10,000 30,000 50,000 100,000

Maximum system gates 56,000 119,000 199,000 257,000

Logic elements (LEs) 576 1,728 2,880 4,992

EABs 3 6 10 12

Total RAM bits 12,288 24,576 40,960 49,152

Maximum user I/O pins 136 171 249 333

Verzeichnis