herunterladen

®

Altera Corporation 1

APEX 20KC

Programmable Logic

Device

February 2004 ver. 2.2 Data Sheet

DS-APEX20KC-2.2

Features...

■

Programmable logic device (PLD) manufactured using a 0.15-µm all-

layer copper-metal fabrication process

– 25 to 35% faster design performance than APEX

TM

20KE devices

– Pin-compatible with APEX 20KE devices

– High-performance, low-power copper interconnect

–MultiCore

TM

architecture integrating look-up table (LUT) logic

and embedded memory

– LUT logic used for register-intensive functions

– Embedded system blocks (ESBs) used to implement memory

functions, including first-in first-out (FIFO) buffers, dual-port

RAM, and content-addressable memory (CAM)

■

High-density architecture

– 200,000 to 1 million typical gates (see Table 1)

– Up to 38,400 logic elements (LEs)

– Up to 327,680 RAM bits that can be used without reducing

available logic

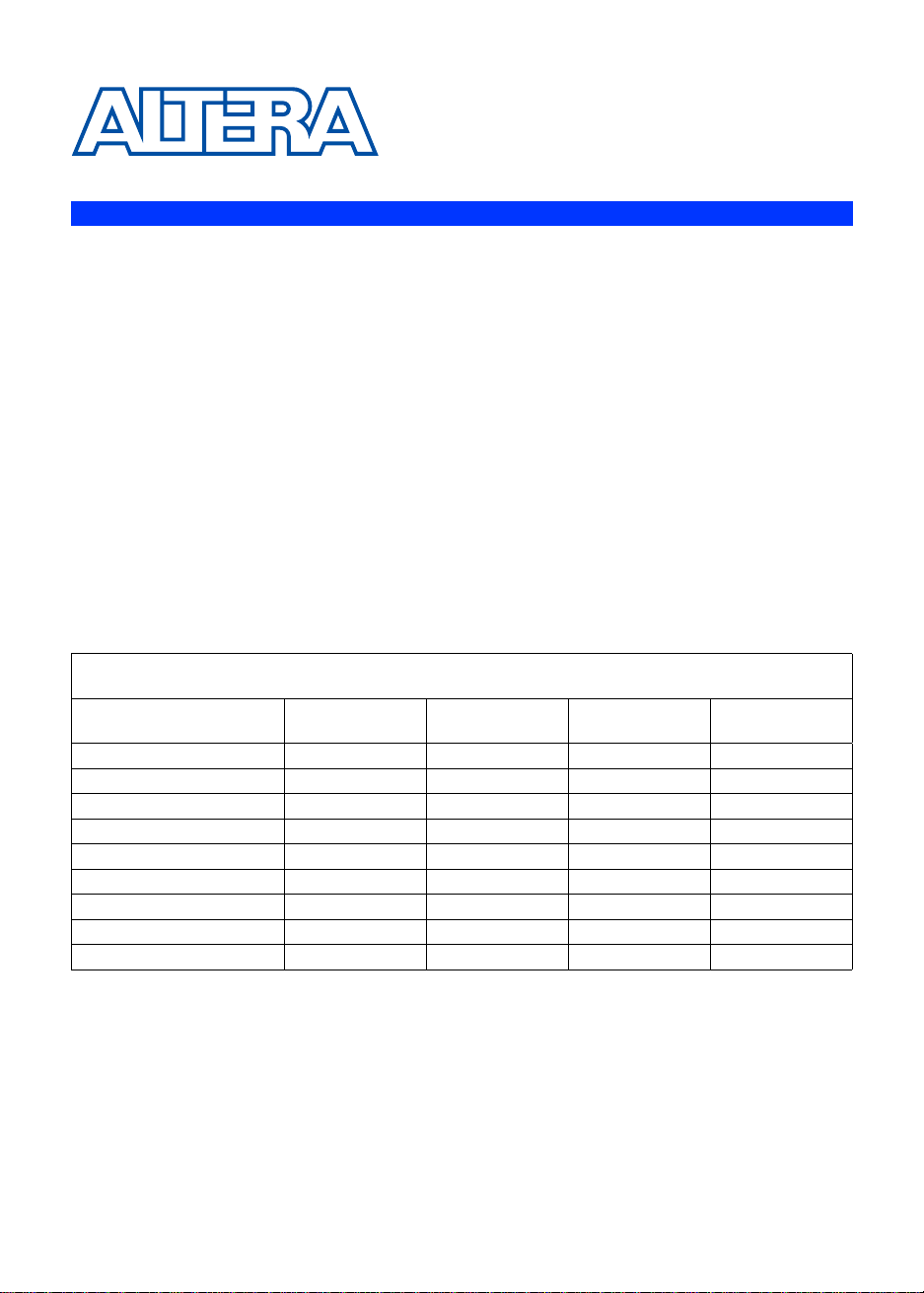

Notes to Table 1:

(1) The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to

57,000 additional gates.

(2) PLL: phase-locked loop.

(3) The -7 speed grade provides the fastest performance.

Table 1. APEX 20KC Device Features Note (1)

Feature EP20K200C EP20K400C EP20K600C EP20K1000C

Maximum system gates 526,000 1,052,000 1,537,000 1,772,000

Typical gates 200,000 400,000 600,000 1,000,000

LEs 8,320 16,640 24,320 38,400

ESBs 52 104 152 160

Maximum RAM bits 106,496 212,992 311,296 327,680

PLLs (2) 2444

Speed grades (3) -7, -8, -9 -7, -8, -9 -7, -8, -9 -7, -8, -9

Maximum macrocells 832 1,664 2,432 2,560

Maximum user I/O pins 376 488 588 708

Verzeichnis

- ・ Abmessungen des Paketumrisses on Seite 4 Seite 87

- ・ Teilenummerierungssystem on Seite 87

- ・ Blockdiagramm on Seite 8 Seite 28 Seite 35

- ・ Beschreibung der Funktionen on Seite 4 Seite 7

- ・ Technische Daten on Seite 48 Seite 54 Seite 56 Seite 57 Seite 58

- ・ Anwendungsbereich on Seite 4 Seite 36 Seite 50 Seite 90